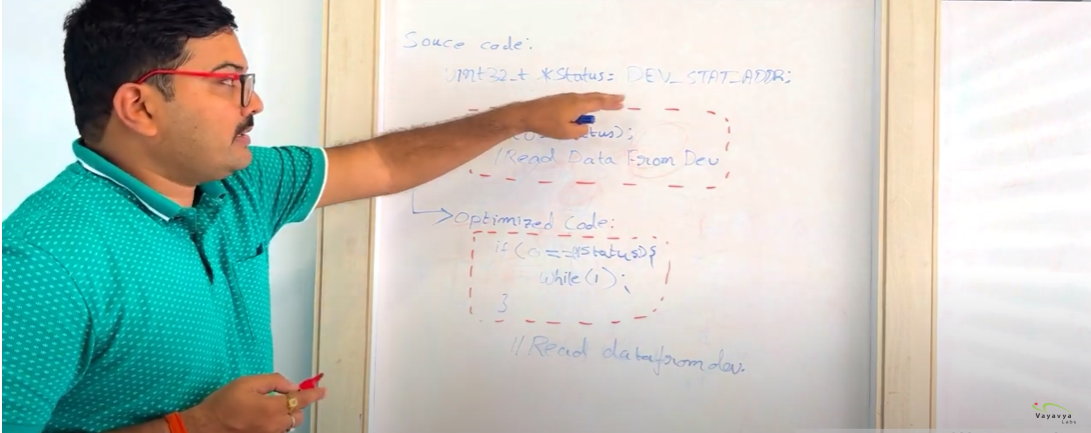

Learn from our Architect, Abhijith Naik- When to use the Volatile Keyword, What syntax to use to represent a volatile object in code, and How to use it.

Digital Twin

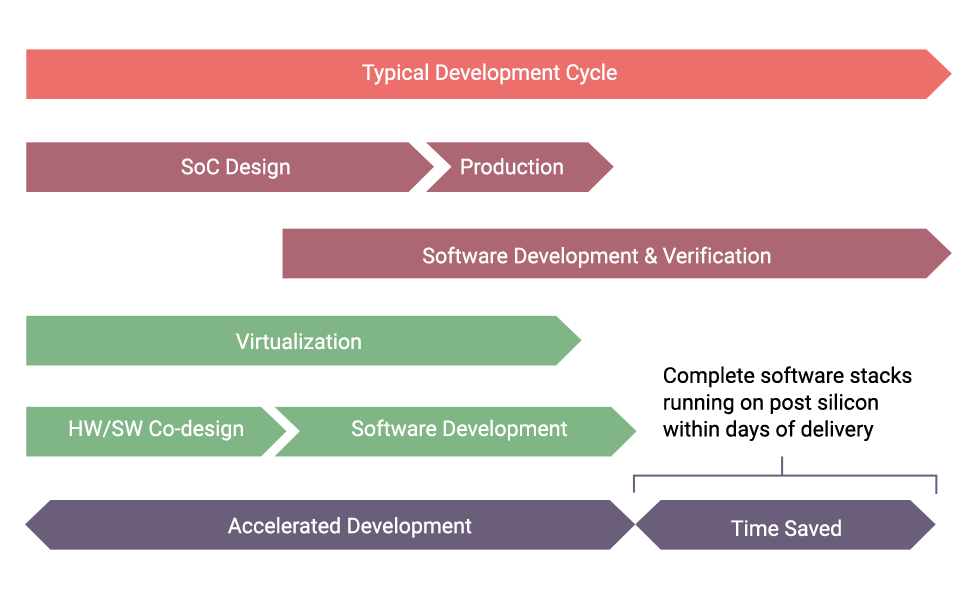

Digital Twin, also known as, Virtual Platform, removes the dependency on physical hardware for the designers.

The design team can explore performance requirements early in the design cycle and ensure consistency between hardware & software verification results for the common tests, eliminating the possibility of misinterpretation.

FEATURES

Model development for Customer’s IP portfolio.

Peripheral modeling & virtual platform integration in SystemC/TLM.

Embedded software bring-up and optimizations.

PSS-HSI specification for Customer’s IP, enabling software-driven verification.

BENEFITS

Complete software development & system testing months earlier

Identify & resolve Hardware/Software compatibility issues early in the design cycle.

Deploy CI/CD process, improve gate-keeping.

Better MC/DC test coverage with error injection.

Effectively utilize large, geographically distributed software teams.

Related Resource

Discover the power of SystemC in hardware design & verification with this blog. Dive into its features & applications as we provide a panoramic overview.

Organizations can adopt digital twins on a scalable and affordable platform thanks to cloud computing, allowing them to make use of this technology's potential

We spoke with our Lead Engineer, Rajat Shetty, who has 5+ years of experience in Digital Twin, to help you better understand the concept and scope.

If you are preparing to join our SystemC team at Vayavya, read this piece of interview with our senior Engineer, Dishant Chauhan.